This article aims to give the reader a detailed understanding of the RISC-V Architecture and will also help in comparing the RISC-V architecture with popular ARM architecture. Before we dive into technical terminologies and start comparing the two architectures, it is important for the reader to understand what is meant by Instruction Set Architecture.

Instruction Set Architecture (ISA) is basically the portion of the machine that is visible to the assembly level programmer or the compiler writer. ISA is where software meets hardware. ISA defines the commands/ instructions that can natively be understood by a machine and its micro-architecture, and it also defines how the instructions are to be stored, accessed, and implemented.

We give instructions to the hardware of the computer using a language that a computer can understand. The computer language is made up of the words called instructions and the vocabulary is called an instruction set. Instruction sets tell us about the function of each instruction and how the instruction is represented in memory (encoding).

The term architecture describes the functional specification of a processor. It describes what functionality the software can rely on the hardware to provide. Architecture does not tell you how a processor is built. It tells you what a processor can do. Micro-architecture on the other hand describes how a processor is built and designed. Micro-architecture defines, the number and size of caches, cycle counts of instructions, pipeline length, and more.

Having understood what ISA is, we now move on to give an overview of RISC-V and ARM architecture.

RISC-V Architecture Overview

RISC-V (pronounced “risk-five”), is an open ISA that is freely available to academia and industry. It builds and improves upon the original Reduced Instruction Set (RISC) Architecture.

RISC-V is the fifth edition of the RISC ISA designs from UC Berkeley. The roman numeral “V” signifies “variations” and “vectors” to support a range of computer architecture research.

Features of RISC-V Architecture

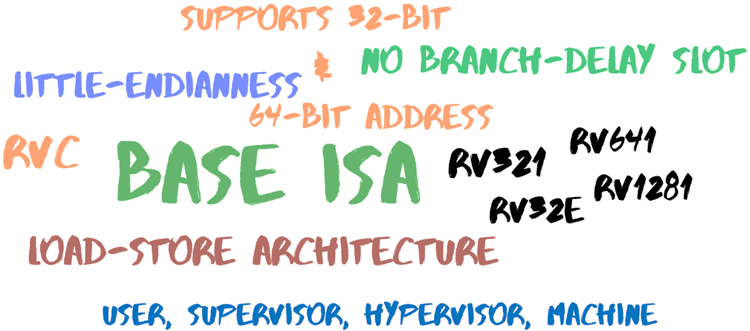

- RISC-V is a load-store architecture, meaning three things: (i) Its arithmetic instructions operate only on registers, (ii) Only load and store instructions transfer data to and from memory, and (iii) Data must first be loaded into a register before it can be operated on.

- RISC-V is not over-architectured/over-optimized for any particular implementation, micro-architectural pattern, or deployment target and hence it is suitable for all computing purposes. It is able to do this because its ISA is broken down into two parts, the base ISA and optional extensions. The base ISA is restricted to contain a minimal set of instructions that are enough to form a compiler target and to satisfy the modern operating systems. The base ISA cannot be re-defined and it is present in any implementation.

- There are additional ISA extensions that can be added to the base ISA depending on the implementation. This allows the RISC-V to also support extensive customization and specialization.

- It is the smallest ISA for 32-bit and 64-bit addresses and uses little-endian byte ordering for the memory system. Little-endian byte ordering means the least significant byte of multi-byte data is stored at the lowest memory address. The LSB is stored first.

- RISC-V uses RVC (RISC-V code compression) technique to improve the program code size and also reduces the number of CPU cycles per instruction at the cost of increasing the number of instructions per program. It sacrifices code density to simplify the implementation circuitry.

- RISC results in large code sizes that are not optimum, particularly for embedded systems because they have a limited instruction memory capacities. To reduce the code size, RISC-V uses its RVC extension. RVC substitutes the common 32-bit instructions with shorter 16-bit instruction encodings. It also has no branch delay slot.

ARM Architecture Overview

ARM originally stands for Acorn RISC Machine but it was later changed to Advanced RISC Machine. It is arguably, the most commonly used processor architecture in the world.

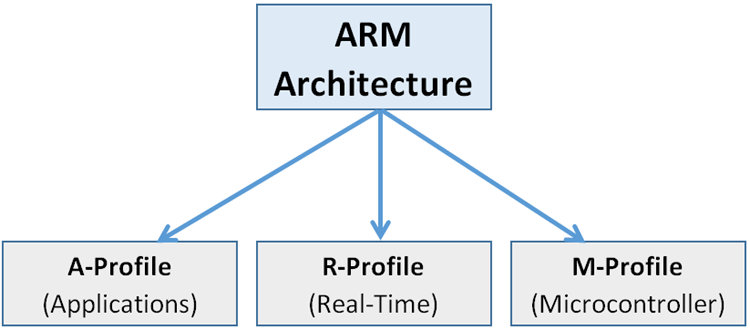

It was first developed by a computer manufacturer called Acorn Computers in the late 1980s for its personal computers. It is a type of RISC architecture. There are 3 different types of Arm architectures for different applications. They are A, R, and M architectures.

A-Profile (Applications): Optimized to run complex operating systems such as Windows and Linux. It offers the highest performance.

R-Profile (Real-Time): Optimized for systems with real-time constraints such as embedded control systems.

M-Profile (Microcontroller): Optimized for low-power devices and is used by many IoT devices

Features of Arm Architecture

- It is a load-store architecture with a 32-bit addressing range.

- Unlike RISC-V, it is not an open-source ISA but a proprietary ISA.

- It uses bi-endian byte-ordering for the memory system. This means an arm processor/machine is able to compute/pass data in both endian formats at a hardware level.

- It uses the Thumb instruction set to reduce the program code size. Thumb is also known as the T32 instruction set, it is used in pre-Armv8 processors.

- It is a mixture of 32-bit and 16-bit length instruction set which has an optimum code density for systems with a memory size and cost constraint like embedded applications. It provides the high performance of a 32-bit instruction set and it almost provides the code density of a 16-bit instruction set.

RISC-V vs ARM

Now that we have an insight on ISA, RISC-V, and ARM, we will compare the two side-by-side based on a variety of factors.

|

Property |

RISC-V architecture |

ARM architecture |

|

Licencing |

Open-source |

Proprietary |

|

RISC Architecture |

✓ |

✓ |

|

Load-store architecture

|

✓ |

✓ |

|

Support 32-bit and 64-bit address spaces

|

✓ |

✓ |

|

Default Endianness

|

Little-endian |

Bi-endian |

|

Code Compression Techniques |

✓ (RVC) |

✓ (Thumb) |

|

Branch delay slot |

none |

none |

Why is RISC-V Considered a Threat to the ARM Architecture?

First of all, RISC-V is open-source while ARM is not. This means that RISC-V is license-free and royalty-free. RISC-V allows the user to extend the ISA with new instructions and innovate the micro-architecture of the RISC-V processors for free but ARM asks the user to pay royalty-fees. This made RISC-V quickly welcomed by many manufacturers.

In terms of complexity, ARM is considered to be more complex than RISC-V. The other reason is that ARM is more over-optimized for mobile-phones than it is for laptops, desktops, and servers. RISC-V is not over-optimized for one particular implementation. It is suitable for all computing systems, from microcontrollers to supercomputers.

Summary

RISC-V and ARM are both RISC ISA Architectures. The former is open-source while the latter is a proprietary ISA. This article first covered the meaning of ISA by breaking down the term into Instruction, Instruction Set, Architecture and describing each of the individual words. Both RISC-V and ARM have their own advantages and it hard to take a side, but the flexibility and open-source nature of RISC-V has made it possible to be adopted faster into the electronics industry, promising a potential future!